# ADA USER JOURNAL

## Volume 35 Number 2 June 2014

## Contents

|                                                                                                                                                     | Page       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Editorial Policy for Ada User Journal                                                                                                               | 70         |

| Editorial                                                                                                                                           | 71         |

| Quarterly News Digest                                                                                                                               | 72         |

| Conference Calendar                                                                                                                                 | 94         |

| Forthcoming Events                                                                                                                                  | 100        |

| Press Release                                                                                                                                       |            |

| "Ada 2012 Language Standard Published in Springer's LNCS and as Free eBook"                                                                         | 104        |

| Articles                                                                                                                                            |            |

| M. Mefteh, N. Bouassida and H. Ben-Abdallah<br>"Feature Model Extraction from Documented UML Use Case Diagrams"                                     | 107        |

| Proceedings of the "Workshop on Mixed Criticality for Industrial Systems" of Ada-Europe 20                                                          | 14 117     |

| R. Davis et al.<br>"PROXIMA: A Probabilistic Approach to the Timing Behaviour of Mixed-Criticality System                                           | ns" 118    |

| A. Alonso and E. Salazar<br>"Toolset for Mixed-Criticality Partitioned Systems: Partitioning Algorithm and Extensibilit<br>Support"                 | y<br>123   |

| P. Lindgren, D. Pereira, J. Eriksson, M. Linder and L.M. Pinho<br>"RTFM-lang Static Semantics for Systems with Mixed Criticality"                   | 128        |

| M. Jan, L. Zaourar, V. Legout and L. Pautet<br>"Handling Criticality Mode Change in Time-Triggered Systems through Linear Programmi                 | ng" 133    |

| O. Cros, F. Fauberteau, L. George and X. Li<br>"Mixed Criticality over Switched Ethernet Networks"                                                  | 138        |

| A. Cohen, V. Perrelle, D. Potop-Butucaru, E. Soubiran and Z. Zhang<br>"Mixed Criticality in Railway Systems: A Case Study on Signaling Application" | 144        |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                           | 148        |

| Ada-Europe Sponsors Inside E                                                                                                                        | Back Cover |

|                                                                                                                                                     |            |

## Editorial Policy for Ada User Journal

## Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

## Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj.*

## **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

## **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

## **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

## **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

## Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

## **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

## Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

## **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

## Editorial

This editorial is being written at the location of the 19th International Conference on Reliable Software Technologies – Ada-Europe 2014, in the heart of Paris, France, after a really intense week. As usual, the five days of the conference provided both very rich technical contents (some of which we start publishing in this issue) as well as a very pleasant networking atmosphere; I would like to congratulate the conference committees for the excellent week we enjoyed!

I also take the opportunity to invite our readers to the next Ada-Europe conference, which will take place in Madrid, Spain, 22-26 June 2015, organised by the Universidad Politécnica de Madrid. More details about Ada-Europe 2015 can be found in the forthcoming events section of the Journal. Also in this section the reader will find updated information on the SIGAda HILT 2014 conference, which will be co-located with the SIGPLAN SPLASH conference, in Portland, Oregon, October 18-21, 2014. And I am very pleased to inform about the next edition of the International Real-Time Ada Workshop, which will take place April 2015, in Vermont, USA. We expect to publish the call for papers of IRTAW 2015 in the next issue of the Journal.

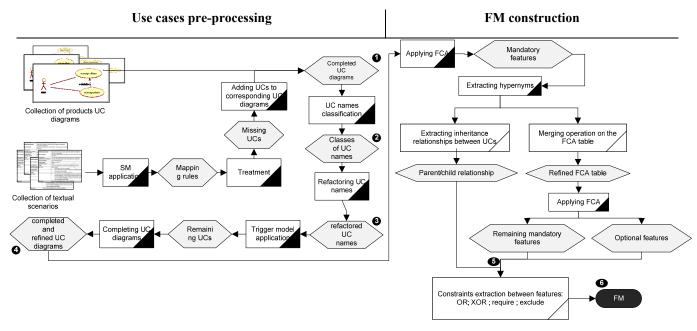

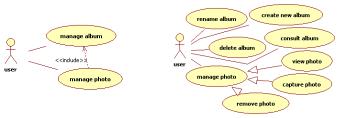

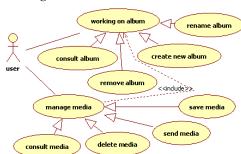

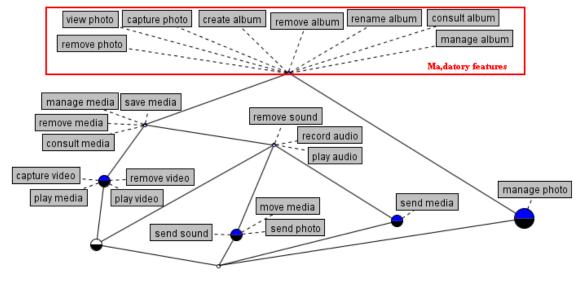

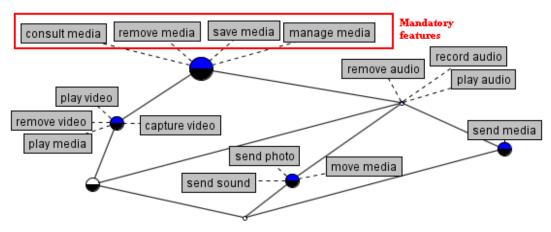

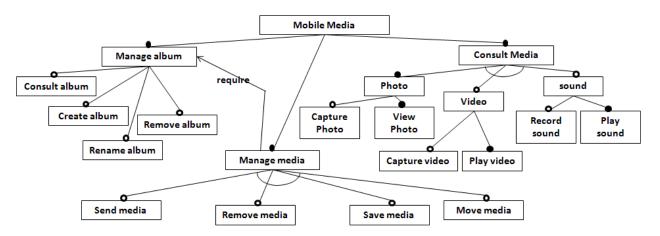

Concerning the technical contents of this issue, the first paper, from a group of authors from the Sfax University, Tunisia and King Abdulaziz University, Saudi Arabia, presents an automated approach to extract the features model from software product lines.

Afterwards, the issue publishes the Proceedings of the "Workshop on Mixed Criticality for Industrial Systems", which took place at Ada-Europe 2014, June 27. The workshop provided a discussion forum on research and practice in Mixed-Criticality Systems, showing how research activities interact with industrial needs. The workshop program consisted of a keynote talk, and two technical sessions.

The keynote talk was given by Albert Cohen, senior research scientist in the PARKAS group at INRIA, France on the topic of "Correct-by-Construction Multiprocessor Programming: A Common Approach for Parallel and Mixed-Critical System Design". Multicore and mixed-criticality are important topics, being even more important to provide safe ways to develop such kind of systems.

The first technical session started with a position paper on the PROXIMA project, on the topic of probabilistic approaches for timing behaviour of mixed-criticality systems, from a group of authors from multiple institutions: the University of York, UK, University of Padova, Italy, Aeroflex Gaisler, Sweden, Sysgo, France, Rapita Systems, UK, Ikerlan, Spain, Airbus Operations, France, INRIA Paris-Rocquencourt, France, Astrium, France, Infineon Technologies, UK and Barcelona Supercomputing Center, Spain. Then, a work from Universidad Politécnica de Madrid, Spain, provided insights in the support for automatic partitioning generation in the MultiPARTES toolset. The third work, from the Luleå University of Technology, Sweden and the CISTER Research Centre, Portugal, described the RTFM-lang approach using compile-time analysis to distinguish critical and non-critical functions and generate the appropriate access mechanisms.

The second session of the workshop started with a work from CEA-LIST, France, Virginia Tech, USA and Telecom Paristech, France, showing how a linear programming approach can be used to generate time-triggered schedules for mode changes in dual-criticality systems. After that, a work from ECE Paris and University Paris-Est, France, analysed how to integrate criticality handling in the IEEE 1588 Precision Time Protocol. And finally, a work from INRIA, Technological Research Institute SystemX, and Alstom Transport, France, presented a case study of mixed-criticality systems, in a signalling railway application.

It was a very rich workshop, with fruitful interaction between participants promoting collaboration between the different communities represented. A very interesting day at the end of the Ada-Europe week.

Luís Miguel Pinho Paris June 2014 Email: AUJ Editor@Ada-Europe.org

## Quarterly News Digest

## Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

## Contents

| Ada-related Events         | 72 |

|----------------------------|----|

| Ada Semantic Interface     |    |

| Specification (ASIS)       | 73 |

| Ada-related Resources      | 74 |

| Ada-related Tools          | 74 |

| Ada-related Products       | 81 |

| Ada and Operating Systems  | 82 |

| References to Publications | 84 |

| Ada Inside                 | 84 |

| Ada in Context             | 85 |

## Ada-related Events

## Ada-Europe 2014 in Paris

From: Dirk Craeynest <Dirk.Craeynest@cs.kuleuven.be> Date: Sun, 4 May 2014 21:29:23 +0200 Subject: 19th Int.Conf. Reliable Software Technologies, Ada-Europe 2014 To: Ada-Europe-attendees@ cs.kuleuven.be

Call for Participation

\*\*\* PROGRAM SUMMARY \*\*\*

19th International Conference on Reliable Software Technologies -Ada-Europe 2014

23-27 June 2014, Paris, France

http://www.ada-europe.org/ conference2014

Organized by Ada-France on behalf of Ada-Europe, in cooperation with ACM SIGAda, SIGBED, SIGPLAN and the Ada Resource Association (ARA)

\*\*\* Online registration open! \*\*\*

All info available on conference web site

Early registration discount until May 31

The 19th International Conference on Reliable Software Technologies - Ada-Europe 2014 takes place in Paris, France, from June 23 to 27, 2014. It is an exciting event with an outstanding technical program, keynote talks, and exhibition from Tuesday to Thursday, and a rich program of workshops and tutorials on Monday and Friday.

The conference is hosted by ECE, a French engineering school located near

the Tour Eiffel, right in the heart of Paris, with convenient connections to all places of interest, and lots of facilities around.

An event not to be missed!

The Ada-Europe series of conferences has become established as a successful international forum for providers, practitioners and researchers in all aspects of reliable software technologies. These events highlight the increased relevance of Ada in safety and security-critical systems, and provide a unique opportunity for interaction and collaboration between academics and industrial practitioners.

Extensive information is available on the conference web site, such as the list of accepted papers and industrial presentations, and detailed descriptions of all workshops, tutorials and keynote presentations.

Also check the conference web site for registration, accommodation and travel information.

Quick overview

- Mon 23 & Fri 27: tutorials

- Tue 24 Thu 26: core program

### Proceedings

- published by Springer

- volume 8454 in Lecture Notes in Computer Science series (LNCS)

- will be available at conference

- Program co-chairs

- Laurent George, LIGM/UPEMLV -ECE Paris, France lgeorge@ieee.org

- Tullio Vardanega, University of Padova, Italy

tullio.vardanega@unipd.it

- Invited speakers

- Robert Lainé, "Lessons Learned and Easily Forgotten", drawing from his many years of experience in space projects leadership at the European Space Agency and EADS Astrium.

- Alun Foster, "From ARTEMIS to ECSEL: Growing a Large Eco-System for High-Dependability Systems", about the results achieved in ARTEMIS and the objectives of the new ECSEL program, as Acting Executive Director and Programme Manager of the ARTEMIS JU.

- Mohamed Shawky, "Future Challenges in Design Tools and Frameworks for

Embedded Systems; Application to Intelligent Transportation Systems", presenting his futuristic work at the Université de Technologie Compiègne.

#### Workshops (full day)

- Workshop on "Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering" (De-CPS 2014),

organized by CEA and Thales

- Workshop on "Mixed Criticality Systems" (WMCIS 2014): Challenges of Mixed Criticality Approaches and Benefits for the Industry, organized by ECE

- Workshop (half day)

- "Ada 2012: le point sur le langage" (Ada 2012: Assessing the Language), a special session in French for software managers who want to learn about the current state of Ada, organized by Ada-France.

#### Tutorials (full day)

- "Robotics Programming", Lars Asplund, Asplund Data, Sweden

- "Introduction to Verification with SPARK 2014", Rod Chapman, Altran UK, Yannick Moy, AdaCore, France

#### Tutorials (half day)

- "Proving Safety of Parallel/Multi-Threaded Programs", Tucker Taft, AdaCore, USA

- "Multicore Programming using Divideand-Conquer and Work Stealing", Tucker Taft, AdaCore, USA

- "Debugging Real-time Systems", Ian Broster and Andrew Coombes, Rapita Systems, UK

- "Developing Mixed-Criticality Systems with GNAT/ORK and Xtratum", Alfons Crespo, Universidad Politécnica de Valencia, Alejandro Alonso, Universidad Politécnica de Madrid, Jon Pérez, Ikerlan, Spain

- "High-Integrity Object-Oriented Programming with Ada 2012", Ben Brosgol, AdaCore, USA

- "Ada 2012 (Sub)type and Subprogram Contracts in Practice", Jacob Sparre Andersen, JSA Research & Innovation, Denmark

- "Technical Basis of Model Driven Engineering", William Bail, The MITRE Corporation, USA

- "An Overview of Software Testing with an Emphasis on Statistical Testing" William Bail, The MITRE Corporation, USA

Papers and Presentations

- 12 refereed technical papers in sessions on Formal Methods, Uses of Ada, Real-Time Scheduling, Applications

- 6 industrial presentations in sessions on Ada in Aerospace, Ada in Railways

- 3 presentations in special "Experience Report" session

- submissions by authors from 22 countries, and accepted contributions from Austria, Canada, Denmark, France, Germany, Italy, Portugal, Republic of Korea, Spain, Sweden, UK, and USA

**GNAT** Retrospective

- 20th anniversary of GNAT as a supported open-source Ada compiler

- started new era for distribution and promotion of Ada language

- retrospective will look back at these important 20 years

Vendor exhibition

- 5 exhibitors already committed: AdaCore, Altran, Ellidiss Software, Rapita Systems, and Squoring Technologies; others expected to confirm soon

- vendor presentation sessions in core program

Social events

- each day: coffee breaks in the exhibition space and sit-down lunches offer ample time for interaction and networking

- Tuesday evening: Welcome Party

- Wednesday evening: Cruise and Conference Banquet, the traditional Ada-Europe banquet will be on board an all-glass luxury boat, cruising along the Seine right in the heart of Paris!

Registration

- early registration discount up to Saturday May 31, 2014

- additional discount for academia, Ada-Europe, ACM SIGAda, SIGBED and SIGPLAN members

- a limited number of student discounts is available

- registration includes copy of printed proceedings at event

- includes coffee breaks and lunches

- three day conference registration includes all social events

- payment possible by credit card, check, or bank transfer

- see registration page for info on novel student waiver program!

Please make sure you book accommodation as soon as possible.

Paris will be very busy in that week.

For more info and latest updates see the conference web site at

<http://www.ada-europe.org/ conference2014>.

## Ada Semantic Interface Specification (ASIS)

## **ASIS to XML Tools**

From: Robert A Duff

<bobduff@shell01.TheWorld.com> Date: Thu, 20 Mar 2014 11:27:44 -0400 Subject: Re: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

The latest GNAT Pro ASIS fully supports Ada 2012. I don't know if that has made it into the GPL version yet.

It will likely be updated to support Ada 2022 (or whatever it will be) when that comes along.

> translates (using ASIS GPL 2012 and my ASIS2XML) to

I didn't know about your ASIS2XML project until now.

Do you know about gnat2xml? It is a similar tool produced by AdaCore. (I wrote it.) It is based on ASIS, and supports Ada 2012. Looking at:

http://gnat-asis.sourceforge.net/ pmwiki.php/Main/ASIS2XML

I see some differences:

- gnat2xml has cross-links. E.g. each name points to the declaration it denotes, and each expression points to its type.

- There is an XML schema, automatically generated by an ASIS-based tool called gnat2xsd.

- Each XML element has a "source location", which tells you the starting and ending line and column numbers for the corresponding source text. The root of the tree has various information, including the name of the source file.

- There is also a mode in which gnat2xml generates XML interspersed with Ada source text, including comments.

I think XML is horrible. But it has the advantage of being standard, and everybody uses it, and there are all sorts of useful XML-based tools out there.

From: Robert A Duff <bobduff@shell01.TheWorld.com>

Date: Fri, 21 Mar 2014 12:07:39 -0400 Subject: Re: Kickstarter for beginning work

on a new open-source Compiler Newsgroups: comp.lang.ada

That's the xml2gnat tool, which backtranslates XML into Ada. It was originally developed for testing purposes: Ada-->XML--Ada ought to produce an Ada program that has identical output to the original.

Then I rewrote the pretty-printer (gnatpp) to use that same Ada-generating code. gnatpp does not use XML, but almost all of the code in xml2gnat is shared by gnatpp.

You could use xml2gnat on modified XML, but you would have to make sure the XML looks like what gnat2xml would generate from some legal Ada. Validating it against the schema using xmllint would help with that. But nobody at AdaCore has ever done that; we use xml2gnat purely for testing gnat2xml. For example, we run all the executable ACATS tests that way (translate the test into XML, then back into Ada, then compile and run the generated Ada, and the output should be identical to the output of the original ACATS test, with the usual "= PASSED =

message).

The first version of xml2gnat left out all the comments, which aren't needed for the above kind of testing. But of course gnatpp can't leave out comments, so now xml2gnat also includes the comments, using the same shared code.

[...]

## The Future of ASIS

From: Jean-Pierre Rosen

<rosen@adalog.fr> Date: Thu, 20 Mar 2014 15:17:26 +0100 Subject: Re: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

> [...]

Since there is currently only one implementation of Ada 2012, and since this implementation's ASIS is following the compiler, the decision was taken that the only sensible path was to let GNAT do the work, and standardize on that.

From: Jean-Pierre Rosen

<rosen@adalog.fr> Date: Fri, 21 Mar 2014 06:23:35 +0100 Subject: Re: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

> Hopefully though, the ASIS WG will come out with the proper specs soon.

That's the problem: there is no ASIS WG anymore. The ARG tried to take over, but it's resources are limited, and better used to the maintenance of the language.

> And FYI, another reason why we need another competing implementation :D

As far as ASIS is concerned, the Gela project was promising. The idea was to have a compiler targeting ASIS, and then

<sup>&</sup>gt; [...]

<sup>&</sup>gt; [...]

make code generation from ASIS. It was sufficiently advanced that AdaControl compiled with it (except for GNAT extensions for Ada 2005/2012), and even passed a good part of its test suite.

Unfortunately, the author turned to other occupations. It would be nice to have volunteers taking over this project.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Fri, 21 Mar 2014 17:51:12 -0500 Subject: Re: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

> [...] Have any private documents made public so that we or others who want to try to implement it, can do? That is, if there are any that are still private.

No. ASIS (unlike the Ada standard) is owned by ISO, and we can't give away their "property". In any case, the updated ASIS standard draft was effectively rejected by the ASIS implementors (by ignoring it and doing their own thing). Vendors have told us outright that they don't think there is any value to an ASIS standard and that they won't support one if it is made. As such, there is no point in putting any more effort into it.

I suggest considering ASIS past Ada 95 as implementation-specific. Perhaps someday there will be agreement on a way forward, but it really only matters for people that want to port ASIS tools. At this point, that community appears to exist solely of J-P Rosen -- everybody else seems to be using GNAT ASIS only (or one of the Atego ASIS implementations only). So there's little point to a standard.

If you disagree, then you need to form your own ASIS WG, put pressure on ASIS vendors to define a consistent set of extensions and ways to plug the many holes in the ASIS standard, and then it's likely that the energy to actually update the standard will materialize. The key here is the pressure on vendors from customers -- they have to see a benefit from having a standard -- they don't see that now.

#### From: Tero Koskinen

<tero.koskinen@iki.fi> Date: Tue, 25 Mar 2014 17:16:43 +0200 Subject: Re: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

>>>> There is also GELA ASIS: http://gela.ada-ru.org/gela\_asis\_ug

>>> Unfortunately, still incomplete and not making progresses any more.

Yes, the project itself is kind of alive (or zombie at least?). Source repository saw commits just 9 days ago:

http://forge.ada-ru.org/gela/browser

And the latest release (0.3.2) is from December 2013:

Volume 35, Number 2, June 2014

http://www.ada-ru.org/files/ gela-asis-0.3.2.tar.bz2

I guess the author is not that active on keeping the documentation up-to-date. :)

(PS: Most of this was provided via #ada@Freenode IRC channel. It is quite good information source for all kinds of informal "news".)

## Ada-related Resources

## **Repositories of Open Source** Software

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Sun May 11 2014 Subject: Repositories of Open Source

software

AdaForge: 8 repositories [1] Bitbucket: 109 repositories [2]

16 developers [2]

Codelabs: 18 repositories [3]

Free(code): 79 [4]

GitHub: 543 repositories [5]

127 developers [6]

Rosetta Code: 596 examples [7]

27 developers [8]

Sourceforge: 229 repositories [9]

[1] http://forge.ada-ru.org/adaforge

[2] http://edb.jacob-sparre.dk/Ada/ on\_bitbucket

[3] http://git.codelabs.ch/

[4] http://freecode.com/search?page=1& submit=Search&with=2880

[5] https://github.com/search? q=language%3AAda&type=Repositories

[6] https://github.com/search? q=language%3AAda&type=Users

[7] http://rosettacode.org/wiki/ Category:Ada

[8] http://rosettacode.org/wiki/ Category:Ada User

[9] http://sourceforge.net/directory/ language%3Aada/

[See also "Repositories of Open Source Software", AUJ 35-1, p. 6. —sparre]

## Ada-related Tools

## **Bound-T: RAM Usage Analysis for AVR-Ada**

From: Vinicius Franchini <viniciusnf@gmail.com> Date: Sun, 19 Jan 2014 10:18:18 -0800 Subject: Ram Usage Newsgroups: comp.lang.ada I'd like to know if there are any way to know how much of ram is been used by my code.

I tried the avr-size, but it gives you just the static ram. The problem is how to evaluate the full memory consumption, including the non-static part.

#### From: Niklas Holsti

<niklas.holsti@tidorum.fi> Date: Mon, 20 Jan 2014 11:40:15 +0200 Subject: Re: Ram Usage Newsgroups: comp.lang.ada

>[...]

For stack consumption you can try a static analyzer such as my Bound-T (www.bound-t.com). This analyzer does not (yet) address the GNAT secondary stack, but, if I remember correctly, there is no secondary stack in GNAT for AVR. I have no suggestions for heap memory usage.

[Since January 2014 Bound-T has been Open Source software. —sparre]

## **Markdown to HTML**

From: Natasha Kerensikova

I have been working on an Ada library that parses lightweight markup languages and render them in various output format (somewhat like pandoc, except I'm not sure my architecture scales easily to a feature set as big as pandoc's).

I wanted to integrate it in the server for my website and let it run in production for a while before formally realising it, however for various reasons it may take a while before I reach that point.

Currently, the library is fully functional with only Markdown front-end and (X)HTML back-end, it passes the official markdown test suite (that I don't distribute because of licence uncertainty) and a decently-covering homegrown test suite (according to gcov, it covers 1112 lines out of 1217 in official markdown frontend, 657/732 lines in markdown extensions, and 348/398 lines in (X)HTML back-end).

Since recently there has been discussions here about Ada for the web, and there's even a FOSDEM talk about it, so maybe Markdown-to-HTML is of interest too.

I would be greatly interested in hearing any comment or criticism or event bug reports about it.

Features request are welcome too, though I can't tell for now when I will manage to look into them. Currently reStructuedText front-end and fully-configurable ODT back-end are on my radar. I can get into the details of how it works internally, but

## Ada-related Tools

I won't bore you with it if it's not necessary.

The code is released under ISC licence and currently available on github at http://github.com/faelys/markup-ada and eventually the "official" fossil repository will be on my aforementioned website.

## **POSIX File Descriptors as** Streams

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Thu, 06 Mar 2014 11:51:59 +0100 Subject: POSIX streams Newsgroups: comp.lang.ada

I've just written a package wrapping a POSIX file descriptor as an Ada stream for use at AdaHeads:

http://repositories.jacob-sparre.dk/ posix-streams

Feel free to reuse it as Beer-Ware or GPLv3.

## ZanyBlue

From: Michael Rohan <michael@zanyblue.com> Date: Sun, 9 Mar 2014 22:08:43 -0700 Subject: ANN: ZanyBlue v1.2.0 Beta Available

Newsgroups: comp.lang.ada

A new release of ZanyBlue is now available: 1.2.0 Beta. This is an Ada library currently targeting localization support for Ada (along the lines of Java properties) with supporting message formatting and built-in localization for about 20 locales.

The properties files are compiled into Ada sources which are then built with your application and used to access application messages at run-time. The run-time locale is used to select localized messages, if they are available.

The changes for this release are:

- Updates for building with GNAT 2013.

- Moved usage of Generic packages to library level (stricted accessibility checks with GNAT2013).

- Dropped definition of "ld run path" definition (created issues on MacOS).

- Updated CLDR data to v24 Release (see cldr.unicode.org).

- Allow localization for +/- characters to be multi-character strings.

- Improved errors messages for invalid zbmcompile command line arguments.

- Implemented message filtering for all Print routines.

- Added directory tree level initialization files for zbtest.

- Bugfixes, e.g., handling OS LANG values with dashes in the encoding.

- Some documentation updates.

- Added a patch to ZanyBlue-ize GNAT GPS 5.2.1 (released with GNAT 2013). The resultant executable is identical to the standard gps but with support for pseudo translation (no real attempt is made to supply localized properties files for GPS).

Please see the project page on Source Forge for download links, documentation, etc,

http://zanyblue.sourceforge.net

This project is licensed under a simple BSD style license.

## Adaino

From: Pablo Rego <pvrego@gmail.com> Date: Tue, 11 Mar 2014 04:26:10 -0700 Subject: Adaino (2.0) released Newsgroups: comp.lang.ada

I am pleased to announce that I released my library for coding Arduino-like boards with Ada using avr-elf-windows, in github for public access. Named Adaino, I just released v.2.0.

https://github.com/pvrego/adaino

## **Request: LEGO Mindstorms EV3 Development Kit**

From: Karen Sarkisyan <karen.sarkisyan@gmail.com> Date: Tue, 11 Mar 2014 02:02:41 -0700 Subject: Ada for Mindstorms EV3 Newsgroups: comp.lang.ada

I'm interested to know if there are some examples of Ada code or developments for the new version of Lego Mindstorms (EV3 Brick). I know that there is much done for NXT, but the question is about present/future of Ada on this new platform. Any ideas? As far as I know, NXT development resources are incompatible with EV3.

Something from AdaCore to use (Open Source)?

## **Emacs Ada Mode**

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Sat, 15 Mar 2014 08:09:29 -0500 Subject: Emacs Ada mode 5.1.1 and wisi 1.0.2 released

Newsgroups: comp.lang.ada

Emacs Ada mode 5.1.1 and wisi 1.0.2 are now available in Gnu ELPA, and on my web page:

http://stephe-leake.org/emacs/ ada-mode/emacs-ada-mode.html

See the NEWS file there for release notes.

The main changes are support for Emacs 24.2 (for Debian stable) and better support for aspects. There are also several bug fixes.

## Ada EL

From: Stephane Carrez <Stephane.Carrez@gmail.com> Date: Wed Mar 19 2014 Subject: Ada EL 1.5.0 is available URL: http://blog.vacs.fr/vacs/blogs/ post.html?post=2014/03/19/ Ada-EL-1.5.0-is-available

Ada EL is a library that implements an expression language similar to JSP and JSF Unified Expression Languages (EL). The expression language is the foundation used by Java Server Faces and Ada Server Faces to make the necessary binding between presentation pages in XML/HTML and the application code written in Java or Ada.

The presentation page uses an UEL expression to retrieve the value provided by some application object (Java or Ada). In the following expression:

#{questionInfo.question.rating}

the EL runtime will first retrieve the object registered under the name questionInfo and look for the question and then rating data members. The data value is then converted to a string.

The new release is available for download at http://download.vacs.fr/ada-el/ada-el-1.5.0.tar.gz

This version brings the following improvements:

- EL parser optimization (20% to 30% speed up).

- Support for the creation of Debian packages.

## Augusta

From: Peter C. Chapin <PChapin@vtc.vsc.edu> Date: Wed, 19 Mar 2014 09:24:36 -0400 Subject: Augusta: An open source Ada 2012 compiler (someday?) Navgroups: comp lang ada

Newsgroups: comp.lang.ada

In another thread Shark8 posted a proposal to build an IDE+compiler for Ada 2012. In his post he notes that having a second open source compiler offering (besides GNAT) for Ada would be good for the Ada community.

## I agree.

GNAT is a fine product but it would enrich the eco-system if there were alternatives. Accordingly I started a pet project for myself to build an Ada 2012 compiler from the ground up which I'm calling "Augusta." The project is here:

https://github.com/pchapin/augusta

I am not as naive as I probably sound. I fully understand that such a project is massive and not likely to actually ever be completed. Fortunately that's not important to me. The project is just a hobby project and its \*real\* purpose is to provide me with a source of entertainment in my off hours. It can fulfill that role perfectly well even if it never amounts to anything. This situation also frees me to make design choices that interest me without feeling the need to justify them rationally. For example Augusta will be written in Scala and will target LLVM. I choose these technologies because I like them and I'd like to learn more about them, not because I think they are somehow the "best" or most logical choices.

I have been planning to announce Augusta's existence to the community at some point but right now the project is 99% talk and 1% action (at most) and I had thought to wait until the balance was a little different. However, Shark8's announcement of his IDE proposal made this seem like a reasonable time. I support his desire to develop such tools and who knows... perhaps Augusta can play some role in his project someday.

Right now Augusta is little more than a place holder with some documents outlining my vision for the project. I have set a release date for myself of December 31, 2020 in an effort to apply some structure to my work. My hope is to have something "interesting" done by that time... although I'm not going to claim it will be full Ada 2012.

In the meantime I've been using Augusta as a source of class examples and student exercises in a compiler course I'm teaching at Vermont Technical College. The work there has been in a sub-project called Allegra which is intended to be a compiler for a series of highly reduced Ada subsets with increasing complexity. In addition to supporting my course, my thought was to use Allegra as a kind of experimentation space for the technologies that will ultimately be part of Augusta. However, I'm not clear how much, if any, of the methods used in Allegra would actually transfer to the more complex Augusta project itself.

Anyway, enough said... I invite anyone who is interested to browse around in the project. Let me know if you have any questions or comments.

[See also "Augusta", AUJ 34-2, p. 68. —sparre]

From: Tero Koskinen

<tero.koskinen@iki.fi> Date: Wed, 19 Mar 2014 20:56:46 +0200 Subject: Re: Augusta: An open source Ada 2012 compiler (someday?) Newsgroups: comp.lang.ada

[...] it is nice to always see someone to start a new open source Ada compiler to "compete" with GNAT (or just for hobby), however in the history all of the earlier attempts have sadly failed. The Open Source Ada community may be too small and diverse for such a project.

One alternative approach could be to persuade one of the existing Ada vendors

to open source their compiler; perhaps even create a (kickstarter) project to collect the money required for it. (Like it was done for Blender.[1])

[1] https://en.wikipedia.org/wiki/ Blender\_%28software%29#History

From: Brian Drummond <brian@shapes.demon.co.uk> Date: Wed, 19 Mar 2014 23:04:50 GMT Subject: Re: Augusta: An open source Ada 2012 compiler (someday?)

Newsgroups: comp.lang.ada

> [https://github.com/pchapin/augusta]

Good luck!

>[...]

LLVM appears to have problems supporting nested (locally declared) subprograms. This appears to be behind slow progress on the Dragonlace project, to use Gnat as an LLVM front end.

Tristan Gingold has recently added an experimental LLVM interface to GHDL (a VHDL compiler; I strongly believe Ada and VHDL users should talk to each other more than they do!) and he also ran into this.

As VHDL makes heavy use of parallel processes, he indicated he would reuse his implementation of processes - essentially closures - to support local subprograms. I don't know the details of how he does this.

(The other advantage of gcc as a backend is that it opens up many more target processors. It would be nice to be able to support both, and the code required in GHDL to support both is really not very much)

From: Jean-Pierre Rosen

<rosen@adalog.fr> Date: Thu, 20 Mar 2014 11:49:27 +0100 Subject: Re: Augusta: An open source Ada 2012 compiler (someday?) Newsgroups: comp.lang.ada

#### >[...]

All those who have been involved in an Ada compiler will tell you that it is a lot more difficult than it appears, unless you stick to the Pascal subset and don't care for validation.

In the early days of Ada, we have seen compilers announcing proudly that they passed 95% of the validation and that delivery was expected in a few weeks they never succeeded to pass the remaining 5%.

For example, and as a test, make sure you are able to understand the implications of 4.3.3 (a nightmare for code generation), or 13.14, or 3.10.2(3/2)...

From: Peter C. Chapin <PChapin@vtc.vsc.edu> Date: Fri, 28 Mar 2014 07:31:36 -0400 Subject: Re: Augusta: An open source Ada 2012 compiler (someday?)

Newsgroups: comp.lang.ada

> [...]

One reason why I choose Scala as an implementation language for Augusta is because I wanted to see if I could productively take advantage of Scala's functional features when writing a serious compiler. As much as I like Ada, I don't think Ada is the most wonderful compiler implementation language imaginable.

For example Scala's algebraic data types and pattern matching make processing trees quite enjoyable and compilers tend to use a lot of trees. Also Scala has good support for creating what the community calls "internal domain specific languages." See for example Graph for Scala (http://www.scala-graph.org/), a library for manipulating graphs (perhaps control flow graphs?) in a arguably elegant way. Finally, of course, there might be interesting ways to use higher order functions. I won't know until I try.

My intention has also been to use LLVM or something similar (C, the JVM, etc) as a back end to reduce the amount of work involved in actually getting executable code generated. I understand it is still necessary to generate code for whatever target I use, but the targets above are all higher level than machine language and so (I anticipate) easier to manage.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Mon, 31 Mar 2014 18:43:28 -0500 Subject: Re: Augusta: An open source Ada

2012 compiler (someday?)

Newsgroups: comp.lang.ada

> [...] As much as I like Ada, I don't think Ada is the most wonderful compiler implementation language imaginable.

But of course Ada is the most wonderful language for everything. :-) :-)

Seriously, though, Ada's strengths are in building large long-lived systems, and any serious attempt to build an alternative Ada compiler has to plan to be a large, longlived system. Add in the advantages in "eating your own dogfood", and it seems like the obvious choice for such a project.

It seems to me that you have other goals, which is of course fine, but it does a disservice to hold up something that's not really designed for long life as a true alternative system.

#### >[...]

What's sad (to me) about this is that Ada has added a lot of stuff since Ada 83 that might be very helpful to implementing an structuring a compiler. But all of the existing Ada front-ends originated in Ada 83 and don't use much in the way of Ada 95 features much less newer versions. (It simply doesn't make sense to rewrite large portions of a compiler's code just because one could -- a lot of the time, rewrites don't actually end up any better than the code they replaced, just swapping a set of known problems for unknown ones.)

## Ada-related Tools

For instance, Ada 2012 has tree containers that exist in large part because of how common such structures are in compilers and similar applications (like XML and HTML). It would be interesting, for instance, to see if an expression tree written using a class-wide node type stored in an indefinite tree container could be efficient enough to use in a compiler implementation. I'd probably at least consider such a structure (which would eliminate all storage management from being a concern) rather than a access-and-variants that we use. Maybe it wouldn't be better, but it would be different.

It also would be nice to predicates, preconditions, null exclusions, and so on, all of which can allow errors to be detected earlier and easier. (Janus/Ada has many self-checking features, but those all require some work on use by the programmers - it would be better to do that just at writing.)

My point is that there is a lot of the possibilities of Ada for compiler construction (especially of Ada 2012) that hasn't really been explored.

(I'm dubious that pattern matching has much to do with the construction of a compiler front-end, either; that's almost exclusively the provence of optimization and code generation, the parts of the compiler you're not planning to work on even though that's the fun part. :-)

## Starting on a new Open Source Compiler and IDE

#### From: Edward R. Fish

<onewingedshark@gmail.com>

Date: Tue, 18 Mar 2014 16:23:57 -0700

Subject: ANN: Kickstarter for beginning

work on a new open-source Compiler

Newsgroups: comp.lang.ada

It is my belief that a new, non-GNAT, open-source [and free] Ada 2012 translator would be a good thing for both the Ada community and the general programming population -- this without even breaking from the traditional approaches. However, I think that a good, quality IDE/PSE could be quite advantageous; offering better projectmanagement, documentation, verification, versioning, and correctness/consistency checking.

The working-copy of the proposal is here:

https://drive.google.com/file/d/ 0BwQVNNshW39cTXVOdWxQaVJ5Wj A/edit?usp=sharing

The link to the Kickstarter is here:

https://www.kickstarter.com/projects/ 871049686/squid-open-source-compilerand-ide-for-the-ada-201 From: Maciej Sobczak <maciej@msobczak.com> Date: Wed, 19 Mar 2014 02:06:05 -0700 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

#### >[...]

#### Short version: this will fail.

#### Long version follows.

The proposal itself is fundamentally broken. You have to be aware that the biggest challenge for the Ada community is that of industry awareness. That is, most of the programming community never heard about Ada and those few that did do not see any reason to invest their time in it. The proposal for starting a significant project with public funding should focus on the rationale to explain why such an investment makes sense. But your proposal does not even attempt to do that. In fact, I think that the word "Ada" appears there fewer times than, say, "Delphi". Leaving aside my own relationship with Ada ;-), I see no reason whatsoever why I should give my money to this project.

You can see this problem in the following way: what will happen if you replace the word "Ada" with "Java" or "Scala" in this proposal? It will still be the same proposal and will still make as much (or as little) sense. Which means that this proposal is \*not\* about Ada. It is about your opinion about how IDE should look like.

Which brings us to another important flaw. The Ada (or Java or Scala, if you decide to replace words) programming language was \*defined\* in terms of text. It \*is\* a text-based language. If you think it is a problem, you will not fix it by reinventing the IDE. You have to redefine the programming language to break its natural ties the text format, but if you take the text-based language and try to work with it as if there is no text, you will fail. This idea (should I write IDEa?) is not even new, it was already practiced. I have had a misfortune to work with something like this in the past and it was utter crap that prevented programmers from doing their work efficiently, because the whole concept isolated the programmers from the existing tools. You will never solve all problems in the IDE, at best you will end up with something that is miserable at some selected aspect of programming work and that instead of enabling programmers to spread their wings, just pisses everybody off.

Which basically already started by fixing parts of the solution before exploring the problem - I'm talking about the precise selection of tools that you have proposed at the very beginning: Delphi + .NET + Mono + InterBase? Really?

No, REALLY?

I just fail to imagine Ada enthusiasts (and you need \*a lot\* of enthusiasm to make something as significant) running to contribute to this.

Sorry.

### From: Peter C. Chapin

<PChapin@vtc.vsc.edu> Date: Wed, 19 Mar 2014 09:02:02 -0400 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

I think the proposal is interesting and I would love to see it succeed. Maciej Sobczak is concerned about the tool isolation that might arise by storing program information in a database of ASTs (or similar). I can see how that might be a problem. An IDE of the proposed nature would definitely require a robust way to import/export traditional source text. A user of such an IDE could then still use traditional version control systems, CI systems, documentation generators, etc.

I understand that environments such as the one proposed have been attempted before. However, just because they didn't work well in the past doesn't mean this attempt must necessarily fail. This attempt could take lessons from the other systems and, perhaps, avoid or work around the issues that caused problems in the past.

The proposal is very ambitious because it provides both a complex IDE and a compiler for Ada 2012. Either one of those projects would be daunting on its own. To the OP: have you considered ways of having the IDE interact with existing compilers? Ada, in particular, does have an ASIS standard that can guide, to some extent, the design of abstract program representations.

I ask this because I have a pet project of my own to write an Ada 2012 compiler from scratch. I will post more about that in another thread to avoid hijacking this one. However, my vision follows the lead of clang, Microsoft's Roslyn C# compiler, and to a lesser extent the Scala compiler. Modern compilers, I believe, should not just slurp up text and output object code. Instead they should be provided as a collection of well documented libraries that can be directly loaded into other applications. This allows applications, such as IDEs, to exchange information with the compiler using abstract representations while at the same time keeping both projects well isolated. See the clang documentation for what I believe is the right way to do it.

Thus as a potential Ada 2012 compiler writer I ask: what sort of APIs would be useful if one wanted to split off the code analysis and generation from the IDE itself and move it into a separately developed library? From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 19 Mar 2014 14:48:18 +0100 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

>[...]

... designed in a [obscene, dying, vendorlocked, the list can easily be continued] language like Delphi. I doubt Ada community will be eager to contribute in Delphi. I did projects in Turbo, Object Pascal and Delphi, never again!

>[...]

Yes, and it is not the compiler alone to interact with the system. No less important components are:

- source code control system

- project management system

- debugger

Project management is especially important for Ada because Ada projects mainly are cross-platform and/or embedded. That require handling of various targets, cross-compilation, linking, uploading (for embedded targets) etc. For example, mere abstraction of OSspecific dynamic linking as done by GNAT project system is a huge task.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Wed, 19 Mar 2014 17:11:32 -0500 Subject: Re: ANN: Kickstarter for beginning

work on a new open-source Compiler Newsgroups: comp.lang.ada

>[...]

Beyond that, I'd be very suspicious of any supposedly general purpose programming system that couldn't be created in itself. There is a great value to eating your own dogfood (as the saying goes). It gets rid of gross usability problems in a hurry, and it reduces risk in the project (as there cannot be show-stopping bugs in the development tools -- you just have to fix any problems that occur).

It does require care to avoid the Catch 22 situation where an old bug is preventing work using the old compiler and a new bug is preventing work using a new compiler so that there isn't any obvious way to do any work. (That happened to us once in the mid-1980s - I had to fix the bug in the old compiler with a binary patch in order to cut the Gordian knot and continue. Have been much more careful about regression testing before abandoning old compiler versions since.)

And of course, we all know that Ada is the best language for creating large projects. An Ada development system is surely a large project. There's a reason that virtually all Ada compilers are largely written in Ada. (Some share backends with other systems, but I don't know of any Ada frontends not written in Ada.)

#### From: Robert A Duff

<body>

<body>

body

<

>...I don't know of any Ada frontends not written in Ada.)

The AdaMagic front end is written primarily in C, although I wrote an optimization pass for it in Ada when I was at Intermetrics. The run-time system is written in Ada.

AdaMagic is used by Green Hills, ADI, and others.

If I were writing an Ada compiler from scratch, I would write it in Ada, using GNAT at first, and then bootstrap. Bootstrapping removes any licensing concerns -- you can use whatever license you want for your own work.

Of course, writing an Ada compiler and an IDE is many, many years of work, as has been pointed out.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Wed, 19 Mar 2014 16:59:48 -0500 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

#### >[...]

It has to provide text import to be considered an Ada 2012 compiler. Ada 2012 requires the compiler to process UTF-8 text in specific formats in order to meet the standard. That's a new requirement for Ada 2012, although as a practical matter any Ada compiler has to be able to process the ACATS and thus needs to have some way to import text.

Unless you're insisting on being an island (and that's not what Ada's about, IMHO), you also need to have export, for no other reason than to allow your code to be used on other Ada compilers when necessary.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Wed, 19 Mar 2014 17:03:40 -0500 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

> I ask this because I have a pet project of my own to write an Ada 2012 compiler from scratch.

Ah, another delusional soul. ;-) Take it from someone who seriously followed that path -- there be dragons. :-) For one thing, if you're at all successful, you'll be stuck there for the rest of your working life. And to get far enough to be at all successful, you'll have to figure out how to deal with lovely things like resolution, visibility, and tyranny of interfaces. Odds are, you'll never get far enough to work on anything interesting.

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Thu, 20 Mar 2014 18:04:29 -0500 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

#### >[...]

> With the "tyranny of interfaces" do you mean in-general like a generic's formal parameters and a subprogram's signature? Or do you mean the construct of the 'interface' keyword?

The interface construct itself. The issues with actually implementing multidispatching are quite daunting, especially given the other requirements of Ada. It clearly can be done; whether I could actually do it is a much more interesting question (particularly without abandoning other properties of our implementation).

#### From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Wed, 19 Mar 2014 09:25:39 -0500 Subject: Re: ANN: Kickstarter for beginning

work on a new open-source Compiler Newsgroups: comp.lang.ada

[...]

1) Why write the new tool in Delphi and not Ada?

The Rationale section "Why implement in Delphi 2007" provides a rationale for implementing in dotnet, not Delphi. There is an Ada compiler for dotnet (I think it needs work, but you are already proposing a huge amount of work, so what's a little more?).

And even that rationale is not convincing. Emacs, Eclipse, GPS are all portable to Linux and Windows; in what other environments do you require running the IDE?

2) The Rationale section "Why Write an Ada Compiler?" provides a justification for writing an IDE plugin, not an Ada compiler.

You can easily extract text from the database and feed it to gnat, or any other Ada compiler.

3) Storing text as correct, structured data:

a) has been tried before; in Rational R1000 (http://en.wikipedia.org/wiki/R1000 - not a very informative link, unfortunately). Did you review any lessons learned from that?

b) Prevents people checking in code so colleagues can answer the question "why doesn't this compile"?

c) Prevents writing skeletons; something I do when starting a totally new project.

4) You don't address "Why write a new IDE rather than a plugin for an existing one?"

IDEs are huge, complex beasts. What you propose to do can be accommodated as a plugin for Eclipse, Emacs, or GPS.

GPS from AdaCore is a nice Ada IDE, but it lacks many features that I find essential on a daily basis, which is why I use Emacs instead. Any new tool you start will be even more limited.

5) Current IDEs (GPS, Eclipse, less so Emacs) use a parsed representation of the source for refactoring, completion, and the other tasks you require in an IDE. That gives the best of both worlds.

6) What is your business plan? You are proposing to directly compete with AdaCore; it is not at all clear from the proposal that you understand what that means.

From: Brian Drummond

<br/>

> One reason to use Delphi rather than Ada is licensing; [...]

Look into that a little more closely ... it is not the case that code \*compiled\* with a GPL compiler is itself GPL'ed.

However it \*is\* the case that code \*linked\* (statically) with a pure GPL runtime system is GPL if the runtime does not have the old "gnat modified GPL" license (aka GMGPL) making an exception by permitting linking to the runtime without extending GPL to the entire executable.

The Libre version of GNAT no longer has GMGPL so you cannot use its runtime in a non-GPL executable.

However, you can build a "zero footprint" Ada program ( without the RTS) as is done for very small embedded MPUs, Atmel AVR. MSP430 etc. and (unless I misread the licensing) these should be GPL-free.

Which means you could in principle substitute another RTS licensed under another license (GMGPL or GPLv3 with the equivalent runtime exception) and link your program (in this case, your own compiler) to that RTS.

And you have to provide such an RTS anyway.

So to use GNAT to bring up your compiler, write the RTS first.

Here's another alternative Ada compiler project...

https://sourceforge.net/projects/ hacadacompiler/

From: Luke A. Guest

<laguest@archeia.com> Date: Thu, 20 Mar 2014 03:21:47 -0700

Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

> One reason to use Delphi rather than Ada is licensing; [...] There is no reason why you cannot use the FSF GNAT, I use this instead of GPL GNAT for the same reason. Plus I think that GPL is not right for libs.

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Thu, 20 Mar 2014 18:35:23 -0500 Subject: Re: ANN: Kickstarter for beginning

work on a new open-source Compiler Newsgroups: comp.lang.ada

[...]

> But storing it as unprocessed text means that you [well, your computer/tools] have to repeat a lot of work (e.g. parsing) again and again.

Parsing is very cheap (Emacs Ada mode does it for indentation); the rest of the compiler is hard.

GNAT is open source; you might be able to split out the parsing phase from the rest, and use that parsed representation as the interface between the IDE and the compiler (I have no idea if the GNAT Ada front end is divided that way).

Non-working code should be kept out of the [main] code-base; this situation can be handled with a chat/messageboard (or similar) sort of functionality -There's \*no\* need to pollute your revisions with code that cannot work.

Not true; sometimes the reason it doesn't compile is related to some other change you made. So you need \_all\_ of the code. And that's what CM system branches are for.

What is in the main branch of your CM is different than what is in some developer's branch; controlling the flow from developer branches to the main (release) branch is a CM issue, not an IDE source code representation issue.

> You can still have the procedure's "is null" spec; and Delphi itself has been generating empty subprograms forever.

Emacs Ada mode skeletons don't compile in GNAT, but the indentation parser accepts them. For example, 'case foo C-e' expands to:

### case Foo is

when => end case;

I can store that in a file, and since it doesn't compile, I'm reminded to finish it.

Can I store that in your database?

[...]

From: Simon Wright

<simon@pushface.org> Date: Fri, 21 Mar 2014 08:17:40 +0000 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

- > case Foo is

- > when =>

- > end case;

The Rational Environment used to include recognisable and storable markers in such cases: for example {statement}. As far as I remember they were displayed in inverse video to make them stand out!

#### From: Erlo

Date: Mon, 24 Mar 2014 21:31:54 +0100 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler Newsgroups: comp.lang.ada

- >> The problem was (at least for the OS/9 cross) that the programs would compile and link, resulting in an exception (Illegal program, I think) when you tried to execute the code.

- > AFAICR the R1000 wouldn't do (the equivalent of) object code generation -"promoting to the code state"? - with placeholders present. But it's a while back!

Been a while for me too! I remember this because it occurred to me that this was a major bummer. It happened more than once that we got these 'illegal program' exceptions on the target caused by placeholders.

When the guys at datamuseum.dk (http://datamuseum.dk/wiki/Rational/ R1000s400) get their machine running, it's worth a test.

From: Edward R. Fish

<onewingedshark@gmail.com>

Date: Thu, 20 Mar 2014 13:30:44 -0700

Subject: Re: ANN: Kickstarter for beginning

work on a new open-source Compiler

Newsgroups: comp.lang.ada

[...]

> 5. This whole project, to me, puts the programmer too far away from the source code. Buries it. That is not a good objective.

That's one problem I'm trying to address, it's not about burying the source, but getting closer to the [underlying] structure and ideas that the code is expressing. An example would be CASE statements, the language mandates that they have complete coverage (individually or via OTHERS) so would it be putting the programmer "too far away from the source" to allow something like "rightclick > show as table" to convert the [possibly nested] CASE statement into a decision table? I mean we already have the mandate that all the possibilities must be covered.

Or, imagine having the ability to visually tinker with a [sub]type; say you have Type Voltage is new Natural range 0 .. 220. that you could have represented with two sliders in the same channel (for First and 'Last) and possibly a tab for indicating [or specifying] the default/uninitialized value. (Perhaps packaging Annex H's "Pragma Normalize\_Scalars" value right there with the type.)

### From: Edward R. Fish

<onewingedshark@gmail.com>

Date: Sun, 23 Mar 2014 23:41:54 -0700

Subject: Re: ANN: Kickstarter for beginning

work on a new open-source Compiler

Newsgroups: comp.lang.ada

#### [...]

My grand, overarching idea was basically:

1) to have the first (and open-source / freely-available) Ada 2012 compiler be written (implementation language rather irrelevant), then

2) have the second be written in Ada 2012 (probably w/ SPARK verification/proving) -- hopefully w/ all annexes (though that's a LOT of work) -and this would be the commercial product, then

3) have that compiler/PSE/IDE available for implementing a verified/proved OS.

Like I said upthread; I believe that we /need/ our foundational tools to be without error... and that means investing in verification & correctness checking.

#### From: Gautier de Montmollin

<gautier.de.montmollin@gmail.com> Date: Thu, 20 Mar 2014 14:35:02 -0700 Subject: Re: ANN: Kickstarter for beginning work on a new open-source Compiler

Newsgroups: comp.lang.ada

Good luck with this ambitious project. A challenge is that at some point the AST knows too much about the program. I've developed a similar system 25 years ago (in Turbo Pascal!) for Ada 83. The pros: no more parsing, compilation is straightforward, links are readily available, the system is able to manage the layout itself, to indent etc. . The cons: formatting rigidity, and if the programmer needs to make a big change, use another package, types and so on, plus all depending changes, he needs to have his program "incorrect" for a while. In my system, it meant export to text, rework the text and then reimport the changed text. Too cumbersome - and tools like GPS offer nowadays navigation tools and autocomplete even in the middle of a such a rework, thanks to smart guessing, and all that at text level...

## Gela

From: Zhu Qun-Ying

<zhu.qunying@gmail.com> Date: Thu, 20 Mar 2014 11:20:33 -0700 Subject: Re: Augusta: An open source Ada 2012 compiler (someday?)

Newsgroups: comp.lang.ada

There is another Ada compiler project, and it seems not developed anymore.

http://gela.ada-ru.org/

http://forge.ada-ru.org/gela/wiki

It is based on the TenDRA compiler.

[See also "The Future of ASIS", earlier in this issue. —sparre]

## ASIS2XML

From: Simon Wright <simon@pushface.org> Date: Sun Mar 23 2014 Subject: ASIS2XML URL: http://asis2xml.sourceforge.net/

## ASIS2XML

ASIS is the Ada Semantic Interface Specification; see

http://www.acm.org/sigada/WG/asiswg/.

This program converts a unit's ASIS representation into XML, so as to make it easier to develop transformational tools using (for example) XSLT.

There is no XML Schema as yet. The output's structure is quite close to that of ASIS, at least in overall terms; for example, an A\_Defining\_Name element in ASIS is represented as a <defining\_name/> element in XML.

This project was originally hosted on SourceForge as part of ASIS for GNAT, and releases up to 20140413 can be found there.

## Copyright

This work is derived from the Node\_Trav component of Display\_Source, which is distributed as a part of the ASIS implementation for GNAT and is Copyright (c) 1995-1999, Free Software Foundation, Inc. The original work in the program is Copyright (c) Simon Wright .

## Licensing

The work is distributed under the terms of the GPL.

## Download

http://sourceforge.net/projects/asis2xml/ files/

## Prerequisites

- GNAT: GPL 2012 or later, or GCC 4.8 or later

- The corresponding GNAT ASIS

- XML/Ada 1.0 or later

Building & Use

See the file INSTALL in the distribution.

## **Excel Writer**

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Sat, 12 Apr 2014 Subject: Excel Writer v.13 URL: http://gautiersblog.blogspot.com/ 2014/04/excel-writer-v13.html

Some recently added features:

- freeze panes

- cell comments

- vertical text alignment

- text orientation

- Ada.Calendar.Time Put/Write and date built-in formats

- background colours

- wrap\_text format option

- Next and Next\_Row

- Text\_IO's New\_Line(lines), Line, Col now available

Excel Writer (Excel\_Out) is a free, standalone, portable, open source package for producing Excel spreadsheets with basic formattings and page layout. It can be used in an "Ada.Text\_IO" fashion, with Put, Put Line and New Line.

Download and more informations here: http://excel-writer.sf.net/

## GNAT GPL and SPARK GPL

From: Jamie Ayre <ayre@adacore.com> Date: Tue, 13 May 2014 09:46:33 -0400 Subject: [AdaCore] Announcing the immediate availability of GNAT and SPARK GPL 2014

To: libre-news@lists.adacore.com

We are pleased to announce the availability of the GNAT and SPARK GPL 2014 toolsets.

GNAT GPL 2014 incorporates more than 120 new features, including Ada 2012 mode enabled by default, many new warnings and improved diagnostics, code generation optimizations, support for symbolic traceback in shared libraries, and improved cross Ada/C++ exception handling.

GNAT GPL 2014 introduces GNAT2XML, for generating XML files from Ada sources, which will help in writing Ada analysis tools quickly in any language. It also provides enhancements to existing tools, including:

- A new version of GNATpp, providing improved Ada layout and greater flexibility

- Support in the GPRbuild multipurpose builder for distributed builds, and better support for parallel builds

It also comes with the latest version of the GPS IDE. The complete list of the major new features in GPS 6.0.1 is accessible here:

http://docs.adacore.com/gps-docs/ release\_notes/build/singlehtml/

SPARK GPL 2014, supporting SPARK 2014, is the first GPL release of the next generation SPARK toolset.

The main features of the new language and toolset are as follows:

- Convergence with Ada 2012 Syntax

- Bigger Language Subset

- Executable Contracts

- Hybrid Verification (the ability to mix unit proof with unit test)

- Formal Container Library

- Generative Mode for Data Dependencies (the ability to perform data flow analysis without explicit global declarations)

- Improved IDE feedback in relation to information flow and verification errors

You will find documentation about the SPARK 2014 toolset here:

http://libre.adacore.com/developers/docu mentation

See in particular the SPARK 2014 Toolset User's Guide to get started. You can also read more about the SPARK 2014 language - including a growing number of tips and tricks here:

http://www.spark-2014.org

Both toolsets can be downloaded from libre.adacore.com.

## **Ada-related Products**

## **GNAT Pro**

From: AdaCore Press Center Date: Tue Feb 25 2014 Subject: AdaCore Releases GNAT Pro 7.2 URL: http://www.adacore.com/press/gnatpro-7-2/

New major release of Ada software development environment includes 120+ new features and extends support across ARM platforms.

NEW YORK, PARIS, and NUREMBERG, Germany, February 25, 2014 - Embedded World Conference AdaCore today announced the next major release of its Ada development environment, GNAT Pro 7.2. Embodying the constant innovation that has driven the product's evolution, this latest GNAT Pro toolsuite incorporates more than 120 new features, many of which are based on customer suggestions. This latest GNAT Pro toolsuite includes several new tools, is available on additional platforms, implements the Ada 2012 language standard by default, and extends its coverage of ARM configurations. The wide range of new or improved functionality brings Ada developers the benefits of increased flexibility, greater efficiency, and broader platform support, all within the context of AdaCore's open source technology and unrivaled support.

GNAT Pro is available on more native and cross platforms than any other Ada development environment, and the 7.2 release adds support for Wind River's VxWorks Cert and LynuxWorks' LynxOS-178 Real-Time Operating Systems (RTOS). It also extends GNAT Pro's ARM support to now include Android, generic Linux on ARM, Bareboard ARM, and Wind River's VxWorks 6 on ARM.

GNAT Pro 7.2 comes with the GPS (GNAT Programming Studio) 6.0 Integrated Development Environment, providing developers with more space for editing and a number of design improvements that bring program-related information within easy reach. The revised look and feel is supported by a new relational database at the heart of the GPS engine, making code navigation much more efficient. It also includes a new version of GNATbench, the Eclipse plug-in. GNATbench 2.8 provides improved support for Wind River's WorkBench, a new source navigation engine, and improved support for the CodePeer static analysis tool.

GNAT Pro 7.2 includes several new tools, including GNAT2XML, which generates XML files from Ada sources and helps developers write Ada analysis tools in any language. Enhancements to existing tools include a new version of GNATpp (pretty printer) with improved Ada layout, and an enhanced GPRbuild multi-purpose builder that offers greater flexibility and support of both distributed and parallel builds.

Other new features of GNAT Pro 7.2 include new warnings and improved diagnostics, code generation optimizations, support for symbolic traceback in shared libraries, and improved cross Ada/C++ exception handling.

"With so many new features and tools in GNAT Pro 7.2, it's difficult to choose which to highlight," said Cyrille Comar, AdaCore EU Managing Director. "I'll pick the new, extremely efficient distributed build capability. Its first industrial user reported that the build time for its complete multi-million SLOC application went down from two hours to five minutes on a Linux farm with dozens of machines. This opens the door to a new level of agility in the development of such massive applications!"

## **GNAT Pro for ARM/Linux**

From: AdaCore Press Center Date: Tue Feb 25 2014 Subject: AdaCore Releases GNAT Pro 7.2 for ARM/Linux

URL: http://www.adacore.com/press/ gnat-pro-7-2-arm-linux/

New major release of AdaCore's development environment extends support for ARM platforms.

NEW YORK, PARIS and NUREMBERG, Germany, February 25, 2014 – Embedded World Conference – AdaCore today announced the release of its latest Ada cross-development environment, GNAT Pro 7.2, for ARM processors running Linux. This GNAT Pro ARM product provides a complete Ada development environment oriented towards embedded systems that require the flexibility and extensive services provided by Linux. Developers of such systems can now exploit the software engineering benefits of the Ada language, including reliability, maintainability, and portability.

"Ada and ARM share at least one major characteristic: they provide a combination of strong industrial maturity and innovative adaptability to their ecosystem," said Cyrille Comar, AdaCore EU Managing Director. "While ARM was systematically addressing the whole spectrum of embedded, low-consumption processors, from the smallest microcontroller to the most powerful multicore, Ada was addressing the rising needs of safer programming techniques through its enhanced support of contract programming. Thanks to GNAT Pro's recent and extensive ARM support, it is now possible to benefit from these combined elements simultaneously."

Incorporating more than 120 new features, this latest GNAT Pro toolsuite implements the Ada 2012 language standard by default, and extends its coverage of ARM configurations to complement GNAT Pro products for VxWorks 6 ARM and bare-board ARM. Some of the new Ada 2012 language features include:

- Contract-based programming (preconditions, postconditions, and type invariants).

- In-out parameters for functions (a much-requested enhancement to the language).

- Enhanced multiprocessor support (multiprocessor affinity and barriers).

- Enhanced integration of concurrency and OOP (re-queue on synchronized interfaces).

- Additional language-defined libraries (vector/matrix libraries).

GNAT Pro 7.2 comes with the GPS (GNAT Programming Studio) 6.0 Integrated Development Environment, providing developers with more space for editing and a number of design changes that bring program-related information within easy reach. The revised look and feel is supported by a new relational database at the heart of the GPS engine, making code navigation much more efficient. GNAT Pro 7.2 also includes a new version of GNATbench, the Eclipse plug-in. GNATbench 2.8 provides a new source navigation engine and improved support for the CodePeer static analysis tool

## **SPARK Pro**

From: AdaCore Press Center Date: Tue May 6 2014

- Subject: Altran and AdaCore Release Next-Generation Static Verification Toolset

- URL: http://www.adacore.com/press/ next-gen-static-verification-toolset/

SPARK Pro 14.0 brings new proof technology and additional language features to developers of high-integrity software.

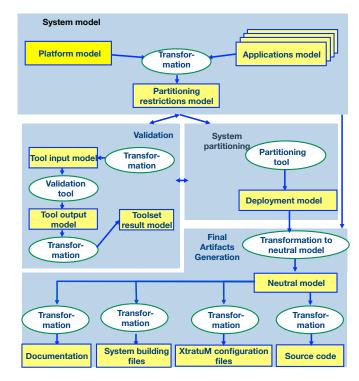

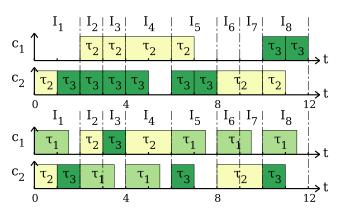

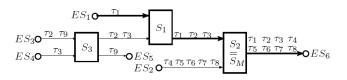

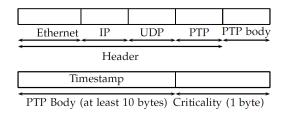

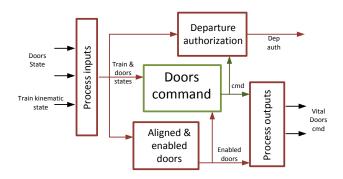

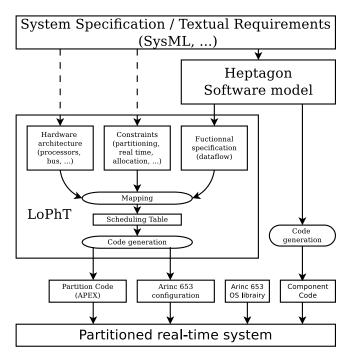

Altran and AdaCore announce the release of the SPARK Pro 14.0 integrated development and verification environment. This product marks a major step forward in software verification technology, providing users with more powerful and easier to use tools that support the latest version of the SPARK language, SPARK 2014. SPARK Pro 14.0 offers an integrated approach to the entire software development and verification lifecycle – bringing software specification, coding, testing and unit verification by proof within a single integrated framework.